# PRELIMINARY DATASHEET

# CGY2120XUH/C1

# **Ultra Low Noise C-Band Amplifier**

# DESCRIPTION

The CGY2120XUH is a high performance GaAs single stage Low Noise Amplifier MMIC designed to operate on the C band.

The CGY2120XUH has an exceptionally low noise figure of 0.5 dB with 13 dB of gain. It can be used in Radar, Telecommunication and Instrumentation applications.

The die is manufactured using OMMIC's Advanced 70 nm gate length high Indium content MHEMT Technology. The MMIC uses gold bonding pads and backside metallisation and is fully protected with Silicon Nitride passivation to obtain the highest level of reliability.

#### FEATURES

- Operating Range : 5 GHz to 7 GHz

- Noise Figure : 0.5 dB at 6 GHz

- Gain : 13.2 dB at 6 GHz

- Input Return Loss : > 6 dB at 6 GHz

- Output Return Loss : > 12 dB at 6 GHz

- Chip size = 1.5 mm x 2.0 mm

- Tested, Inspected Known Good Die (KGD)

- Samples Available

#### APPLICATIONS

- Radar

- Instrumentation

- Telecommunications

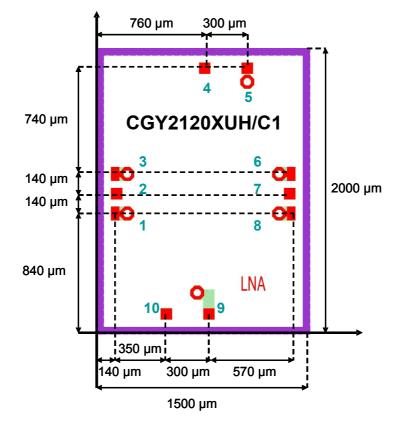

Block Diagram of the CGY2120XUH Low Noise Ampliifier

PRELIMINARY DATASHEET

# CGY2120XUH/C1

2/8

$T_{amb}$  = 25 °C unless otherwise specified.

| Symbol           | Parameter            | Conditions                    | MIN. | MAX. | UNIT |

|------------------|----------------------|-------------------------------|------|------|------|

| V <sub>DD</sub>  | Drain voltage        |                               | 0    | 1.2  | V    |

| I <sub>D</sub>   | Total Drain current  |                               |      | 55   | mA   |

| V <sub>GG</sub>  | Gate supply voltage  | V <sub>D</sub> open-circuited | -2.5 | 0    | V    |

| T <sub>stg</sub> | Storage temperature  |                               | -55  | +150 | °C   |

| Tj               | Junction temperature |                               |      | +150 | °C   |

| T <sub>amb</sub> | Ambient temperature  |                               | -40  | +85  | °C   |

#### THERMAL CHARACTERISTICS

| Symbol               | Parameter                                                               | Value | UNIT  |

|----------------------|-------------------------------------------------------------------------|-------|-------|

| R <sub>th(j-a)</sub> | Thermal resistance from junction to backside ( $T_a = 25 \ ^{\circ}C$ ) | TBD   | ° C/W |

# DC & RF CHARACTERISTICS

$T_{amb}$  = 25 °C, On-wafer measurement results, using 50  $rac{}{s}$  RF probes unless stated otherwise.

| Symbol          | Parameter           | Conditions | MIN. | TYP.  | MAX. | UNIT |  |  |

|-----------------|---------------------|------------|------|-------|------|------|--|--|

| DC chai         | DC characteristics  |            |      |       |      |      |  |  |

| V <sub>DD</sub> | Drain voltage       |            |      | 1     | +1.2 | V    |  |  |

| I <sub>DD</sub> | Drain current       |            |      | 50    |      | mA   |  |  |

| $V_{\text{GG}}$ | Gate supply voltage |            | -2.5 | -0.15 | 0    | V    |  |  |

| RF char         | acteristics         |            |      |       |      |      |  |  |

| BW              | Useful bandwidth    |            | 5    |       | 7    | GHz  |  |  |

| Gain            | Reference Gain      | F = 6 GHz  |      | 13.2  |      | dB   |  |  |

| S11             | Input return loss   |            |      | -6.8  | -6   | dB   |  |  |

| S22             | Output return loss  |            |      | -12   | -6   | dB   |  |  |

| S12             | Isolation           | F = 6 GHz  |      | -19   |      | dB   |  |  |

| NF              | Noise Figure        | F = 6 GHz  |      | 0.5   |      | dB   |  |  |

**Caution :** This device is a high performance RF component and can be damaged by inappropriate handling. Standard ESD precautions should be followed. OMMIC document "OM-CI-MV/ 001/ PG" contains more information on the precautions to take.

3/8

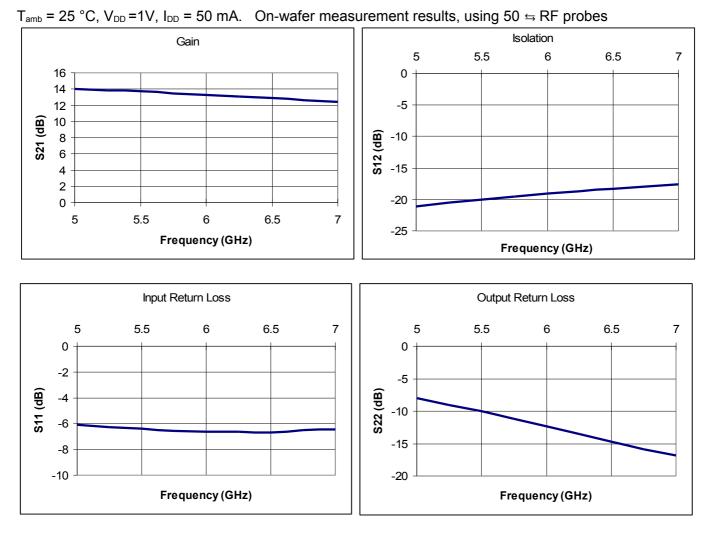

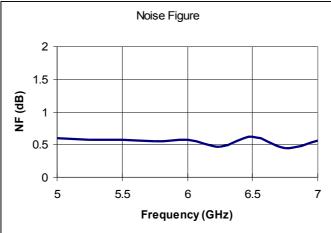

# **MEASURED PERFORMANCE**

**NB** :This product was originally designed to achieve optimal matching and NF performances with bondwires on both ends of the circuit, whereas the presented results were obtained on wafer, using 50 s RF probes.

4/8

#### CGY2120XUH/C1 TYPICAL SCATTERING PARAMETERS

$T_{amb}$  = 25 °C,  $V_{DD}$  =1V,  $I_{DD}$  = 50 mA. On-wafer measurement results, using 50  $rac{}{\simeq}$  RF probes

| Frequency<br>(GHz) | S11  (dB) | Ang S11 (°) | S12  (dB) | Ang S12 (°) | S21  (dB) | Ang S21 (°) | S22  (dB) | Ang S22 (°) |

|--------------------|-----------|-------------|-----------|-------------|-----------|-------------|-----------|-------------|

| 4                  | -4.823    | -80.1       | -24.05    | 132.1       | 14.28     | 155.9       | -4.839    | -90.55      |

| 4.25               | -5.201    | -86.35      | -23.13    | 124.5       | 14.25     | 147.4       | -5.589    | -97.05      |

| 4.5                | -5.529    | -91.68      | -22.42    | 117.6       | 14.2      | 139.9       | -6.326    | -103.3      |

| 4.75               | -5.919    | -96.25      | -21.65    | 110.7       | 14.09     | 131.9       | -7.209    | -110.2      |

| 5                  | -6.112    | -100.1      | -21.07    | 104.7       | 14.01     | 125.2       | -8.054    | -116.9      |

| 5.25               | -6.289    | -103.2      | -20.5     | 98.56       | 13.84     | 118.3       | -9.026    | -124.2      |

| 5.5                | -6.398    | -106.5      | -20       | 93.02       | 13.72     | 112.1       | -10.03    | -132        |

| 5.75               | -6.556    | -108.1      | -19.52    | 87.41       | 13.43     | 105.9       | -11.14    | -140.3      |

| 6                  | -6.655    | -110.7      | -19.09    | 82.05       | 13.29     | 99.46       | -12.33    | -149.7      |

| 6.25               | -6.648    | -112.4      | -18.67    | 77.28       | 13.07     | 94.07       | -13.5     | -160.3      |

| 6.5                | -6.664    | -114.3      | -18.32    | 72.41       | 12.85     | 88.19       | -14.68    | -172        |

| 6.75               | -6.537    | -116.1      | -17.96    | 67.58       | 12.64     | 83.06       | -15.87    | 174.1       |

| 7                  | -6.469    | -118        | -17.63    | 62.74       | 12.41     | 77.66       | -16.88    | 158.4       |

| 7.25               | -6.312    | -120        | -17.29    | 57.95       | 12.17     | 72.96       | -17.59    | 140.7       |

| 7.5                | -6.243    | -121.6      | -16.97    | 53.27       | 11.92     | 67.77       | -17.84    | 121.9       |

| 7.75               | -6.087    | -123.3      | -16.68    | 49.11       | 11.68     | 63.06       | -17.5     | 104.6       |

| 8                  | -5.959    | -125.3      | -16.49    | 45.39       | 11.42     | 58.21       | -16.78    | 90.01       |

5/8

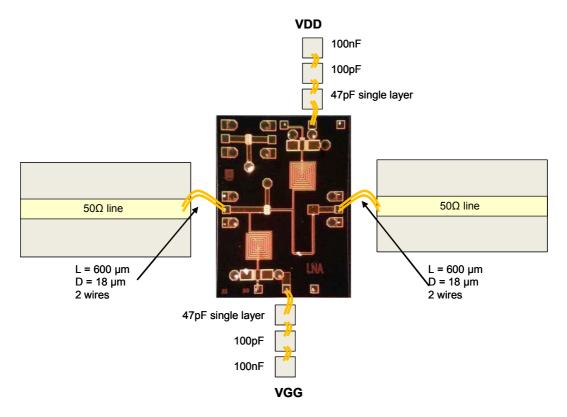

#### **APPLICATION INFORMATION**

#### **Typical application scheme**

A reference module layout is shown below, where RF input and output microstrip transmission lines are used. However, coplanar transmission lines with similar performance may also be used. All path lengths and physical sizes of the components should be minimized.

All RF input and output bonding inductances should be minimized to give the best performance. Overall wire length should be kept as small as possible to reduce parasitic inductance. Higher RF input / output inductance may result in a degradation of gain and match. Ribbon bonding technique can also be used.

All others bondings (pads  $V_{DD}$  and  $V_{GG}$ ) should be kept as short as possible.

Decoupling 47 pF and 100 pF chip capacitors (close to the chip) and 100 nF chip or SMD\* capacitors (positioned at around 4mm from the chip) are used to improve the power supply rejection.

The chip itself has via holes connecting the front side to the back side of the chip. A good RF grounding connection should be maintained between the backside of the chip and system ground. It is extremely important to use an uninterrupted ground plane. AuSn or silver conductive epoxy material can be used for die attachment.

#### CGY2120XUH/C1 module layout : Microstrip assembly

#### \*Surface Mount Devices

6/8

#### **OPERATING AND HANDLING INSTRUCTIONS**

The CGY2120XUH/C1 is a very high performance MHEMT device and as such, care must be taken at all times to avoid damage due to inappropriate handling, mounting and biasing conditions.

#### **1- Power Supply Sequence**

The following power supply sequence is recommended.

- a) Make sure the transient peaks from DC supply voltages do not exceed the limiting values.

- b) Pinch off the device by setting  $V_{GG}$  to -2V.

- c) Increase  $V_{DD}$  to +1V

- d) Increase the gate voltages V<sub>GG</sub> slowly from -2V until the drain current reaches respectively 50 mA.

- e) Apply the RF input signal.

#### 2- Mounting and ESD handling precautions

For high performance Integrated Circuits, such as the CGY2120XUH/C1, care must be taken when mounting GaAs MMICs so as to correctly mount, bond and hence obtain the most reliable long-term operation. The temperature, duration and material compatible with GaAs MMICs and the precautions to be taken are described in OMMIC's document "OM-CI-MV/001/PG", entitled, "Precautions for III-V products".

#### **PAD CONFIGURATION**

PRELIMINARY DATASHEET

# CGY2120XUH/C1

7/8

#### PAD POSITION

| SYMBOL PAI      |     | COOR | DINATES | DESCRIPTION                                                                   |  |

|-----------------|-----|------|---------|-------------------------------------------------------------------------------|--|

| STWDUL          | PAD | Х    | Y       |                                                                               |  |

| GND             | 1   | 140  | 840     | Connected to ground with on-chip via hole                                     |  |

| IN              | 2   | 140  | 980     | RF input                                                                      |  |

| GND             | 3   | 140  | 1120    | Connected to ground with on-chip via hole                                     |  |

| V <sub>DD</sub> | 4   | 760  | 1860    | Drain supply voltage, must be decoupled to ground using external capacitor(s) |  |

| GND             | 5   | 1060 | 1860    | Connected to ground with on-chip via hole                                     |  |

| GND             | 6   | 1360 | 1120    | Connected to ground with on-chip via hole                                     |  |

| OUT             | 7   | 1360 | 980     | RF Output                                                                     |  |

| GND             | 8   | 1360 | 840     | Connected to ground with on-chip via hole                                     |  |

| GND             | 9   | 790  | 140     | Connected to ground with on-chip via hole                                     |  |

| $V_{GG}$        | 10  | 490  | 140     | Gate supply voltage, must be decoupled to ground using external capacitor(s)  |  |

#### **MECHANICAL INFORMATION**

| PARAI                  | METER                                                  | VALUE                                          |  |

|------------------------|--------------------------------------------------------|------------------------------------------------|--|

| Size                   |                                                        | 1500 x 2000 μm                                 |  |

| Thickness              |                                                        | 100 μm                                         |  |

| Backside material      |                                                        | TiAu                                           |  |

| Passivation            |                                                        | PECVD deposited Si <sub>3</sub> N <sub>4</sub> |  |

|                        | GND RF                                                 | 80 x 100 μm                                    |  |

| Bonding pad dimensions | IN, OUT, V <sub>DD</sub> , V <sub>GG</sub> ,<br>GND DC | 80 x 80 μm                                     |  |

### NOTE

The die size and all pad positions refer to the mask layout, with (X=0, Y=0) at the bottom left corner of the layout. For each pad, the (X,Y) coordinates refer to the center of the pad.

Wafers are diced by sawing, with a sawline width of 35  $\mu$ m (± 5  $\mu$ m). A misalignment of the sawline with the middle of the dicing street (± 20  $\mu$ m on all sides) may also result in a variation of ± 20  $\mu$ m of the actual positions of the pads on the diced chip and an additional tolerance of ± 40  $\mu$ m on the die size.

PRELIMINARY DATASHEET

#### CGY2120XUH/C1

8/8

#### DEFINITIONS

#### Limiting values definition

Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 60134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

#### **Application information**

Applications that are described herein for any of these products are for illustrative purposes only. OMMIC makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

#### DISCLAIMERS

#### Life support applications

These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. OMMIC's customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify OMMIC for any damages resulting from such application.

#### **Right to make changes**

OMMIC reserves the right to make changes, without notice, in the products, including circuits, standard cells, and/or software, described or contained herein in order to improve design and/or performance. OMMIC assumes no responsibility or liability for the use of any of these products, conveys no licence or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified.

#### ORDERING INFORMATION

| Generic type | Package type | Version | Description                      |

|--------------|--------------|---------|----------------------------------|

| CGY2120XUH   | Bare Die     | C1      | Ultra Low Noise C-Band Amplifier |

Document History : Version 1.0, Last Update 20/12/2012