ЦАП Analog Devices AD9161BBCZ, 11-bit, RF, 12 GSPS

| Resolution | 11 bit |

| Part number | AD9161BBCZ |

| Manufacturer | Analog Devices, Inc. |

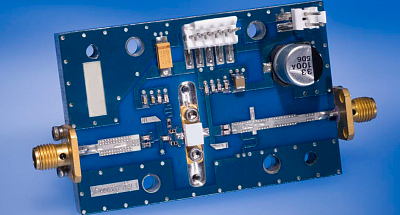

Высокоскоростной ЦАП AD9161BBCZ предназначен для прямого синтеза ВЧ сигналов до 7.5 GHz в системах связи и радиолокации.

Микросхема имеет разрешение 11 bit и ядро на основе quad-switch архитектуры с интерполяцией до 24×.

Интерфейс JESD204B с до восьми линиями обеспечивает гибкую полосу пропускания и скорость передачи данных.

Встроенный ЦАП тока с программируемым выходным током упрощает согласование с внешней ВЧ обвязкой.

Многоканальные режимы интерполяции и цифровая обработка позволяют оптимизировать энергопотребление и спектральные характеристики тракта.

| Resolution | 11 bit |

| Part number | AD9161BBCZ |

| Manufacturer | Analog Devices, Inc. |

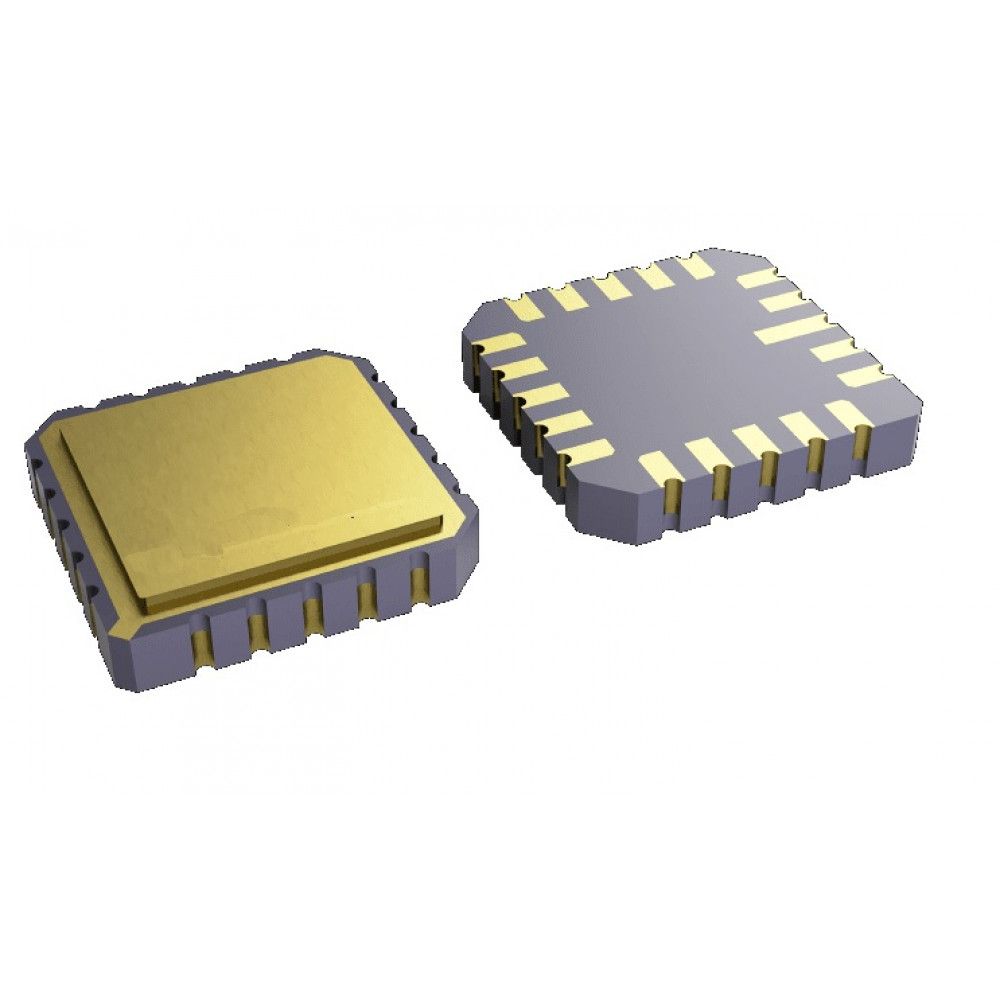

| Package size | 11 mm × 11 mm × 0.95 mm |

| Package type | 169-ball CSP_BGA |

| Converter type | RF Digital-to-Analog Converter |

| Interface type | JESD204B SERDES, SPI |

| Data input format | 2s Comp. |

| Number of channels | 1 |

| Package ball pitch | 0.8 mm |

| SYNC_VDD_3P3 (max) | 3.465 V |

| SYNC_VDD_3P3 (min) | 3.135 V |

| SYNC_VDD_3P3 (typ) | 3.3 V |

| JESD204B lanes (max) | 8 |

| DAC update rate (min) | 1.5 GSPS |

| Interpolation factors | 2×, 3×, 4×, 6×, 8×, 12×, 16×, 24× |

| Gain temperature drift | 105 ppm/°C (typ) |

| I/O supply IOVDD (max) | 3.465 V |

| I/O supply IOVDD (min) | 1.71 V |

| I/O supply IOVDD (typ) | 2.5 V |

| Storage temperature range | −65 °C to +150 °C |

| Internal reference voltage | 1.19 V (typ) |

| Integral nonlinearity (INL) | ±2.7 LSB |

| SERDES supply VDD_1P2 (max) | 1.326 V |

| SERDES supply VDD_1P2 (min) | 1.14 V |

| SERDES supply VDD_1P2 (typ) | 1.2 V |

| SYNCOUT output offset voltage | 1.15 V to 1.27 V |

| Digital core supply DVDD (max) | 1.326 V |

| Digital core supply DVDD (min) | 1.14 V |

| Digital core supply DVDD (typ) | 1.2 V |

| Differential nonlinearity (DNL) | ±1.7 LSB |

| Full-scale output current (max) | 41.3 mA |

| Full-scale output current (min) | 7.37 mA |

| Full-scale output current (typ) | 8 mA |

| Programmable output current range | 8 mA to 38.76 mA |

| Analog supply voltage VDD12A (max) | 1.326 V |

| Analog supply voltage VDD12A (min) | 1.14 V |

| Analog supply voltage VDD12A (typ) | 1.2 V |

| Clock input differential impedance | 90 Ω (typ) |

| Thermal resistance θJA (BC-169-2) | 14.6 °C/W |

| Thermal resistance θJC (BC-169-2) | 0.02 °C/W |

| DAC update rate (max, direct clock) | 6.4 GSPS |

| Reference voltage temperature drift | 75 ppm/°C (typ) |

| SFDR @ fDAC=5000 MSPS, fOUT=500 MHz | −75 dBc (typ) |

| SYNCOUT differential output voltage | 350 mV to 450 mV |

| Clock supply voltage VDD12_CLK (max) | 1.326 V |

| Clock supply voltage VDD12_CLK (min) | 1.14 V |

| Clock supply voltage VDD12_CLK (typ) | 1.2 V |

| Differential clock input power range | −20 dBm to +10 dBm |

| Gain error (with internal reference) | −1.7% |

| SFDR @ fDAC=5000 MSPS, fOUT=1000 MHz | −65 dBc (typ) |

| SFDR @ fDAC=5000 MSPS, fOUT=2000 MHz | −70 dBc (typ) |

| Analog supply voltage VDD25_DAC (max) | 2.625 V |

| Analog supply voltage VDD25_DAC (min) | 2.375 V |

| Analog supply voltage VDD25_DAC (typ) | 2.5 V |

| Operating temperature range (ambient) | −40 °C to +85 °C |

| Negative analog supply VNEG_N1P2 (max) | −1.14 V |

| Negative analog supply VNEG_N1P2 (min) | −1.26 V |

| Negative analog supply VNEG_N1P2 (typ) | −1.2 V |

| Direct RF synthesis bandwidth (Mix-Mode) | 1.5 GHz to 7.5 GHz |

| JESD204B interface lane rate (full rate) | 3 Gbps to 6.25 Gbps |

| JESD204B interface lane rate (half rate) | 6 Gbps to 12.5 Gbps |

| Maximum junction temperature @ fDAC=6 GSPS | 105 °C |

| JESD204B interface lane rate (oversampling) | 1.5 Gbps to 3.125 Gbps |

| Clock input common-mode voltage (AC-coupled) | 0.6 V (typ) |

| Direct RF synthesis bandwidth (2× NRZ mode) | DC to 6 GHz |

| Maximum junction temperature @ fDAC≤5.1 GSPS | 110 °C |

| JESD204B interface lane rate (2× oversampling) | 0.750 Gbps to 1.5625 Gbps |

| Effective DAC update rate (with 2× interpolator) | 12.8 GSPS |

| RESET, CS, SCLK, SDIO logic low input level (max) | 0.3 × IOVDD |

| RESET, CS, SCLK, SDIO logic high input level (min) | 0.7 × IOVDD |

| Direct RF synthesis bandwidth (baseband 1× bypass) | DC to 2.5 GHz |

| SFDR @ fDAC=5000 MSPS, fOUT=4000 MHz, FIR85 enabled | −55 dBc (typ) |

| Noise spectral density @ fDAC=5000 MSPS, fOUT=550 MHz | −157 dBm/Hz (typ) |

| Noise spectral density @ fDAC=5000 MSPS, fOUT=960 MHz | −155 dBm/Hz (typ) |

| Noise spectral density @ fDAC=5000 MSPS, fOUT=1990 MHz | −155 dBm/Hz (typ) |

| Power dissipation @ 5 GSPS, NCO mode, FIR85 disabled, NCO on | 1.3 W to 1.83 W |

| Power dissipation @ 3 GSPS, 2× NRZ, 2× interpolation, NCO on | 2.1 W (typ) |

| Spurious-Free Dynamic Range (SFDR) @ fDAC=5000 MSPS, fOUT=70 MHz | −82 dBc (typ) |

| Power dissipation @ 5 GSPS, 2× NRZ, 4× interpolation, FIR85 enabled, NCO on | 2.58 W (typ) |

Предлагаем ЦАП Analog Devices AD9161BBCZ, 11-bit, RF, 12 GSPS на выгодных условиях с полной технической поддержкой. Проверим наличие, поможем подобрать аналог.

Получить коммерческое предложение или оформить заказ:

8 800 301-96-04 info@fregat.ru

Для разработчиков новой продукции возможен заказ образца!