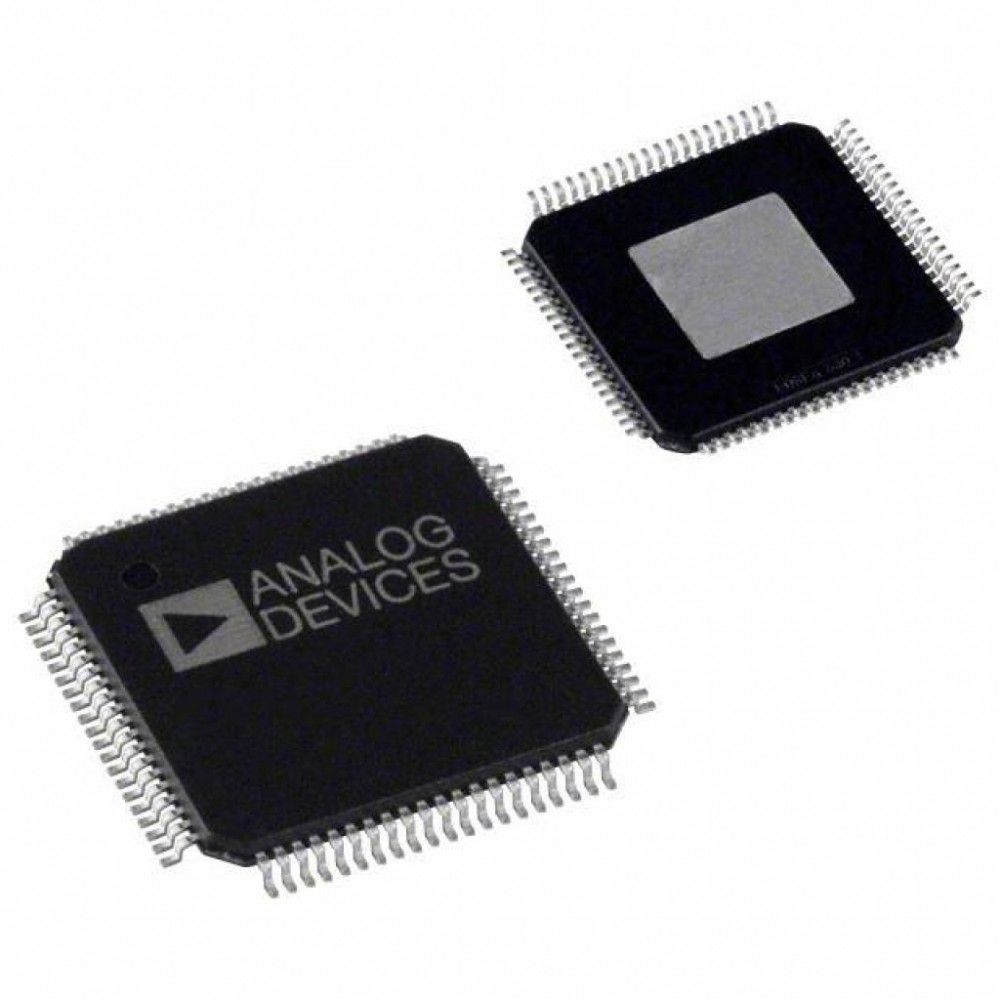

ЦАП Analog Devices AD9777BSVZRL, 16-разрядный, двухканальный, интерполирующий TxDAC+

| Resolution | 16 bit |

| Output type | Current - Unbuffered, differential |

| Internal PLL | Integrated clock multiplier with programmable divider |

AD9777BSVZRL представляет собой двухканальный 16-разрядный интерполирующий ЦАП семейства TxDAC+ с максимальной частотой обновления до 400 MSPS.

Устройство интегрирует цифровые фильтры 2×/4×/8× и блок цифровой квадратурной модуляции с режимами fS/2, fS/4 и fS/8.

ЦАП обеспечивает программируемый полный ток выхода 2–20 mA и широкий динамический диапазон для многоканальных систем связи.

Встроенный PLL-множитель тактовой частоты и делитель упрощают синхронизацию с внешними источниками.

Микросхема работает от одного источника 3.1–3.5 V и содержит встроенный опорный источник 1.20 V.

| Resolution | 16 bit |

| Output type | Current - Unbuffered, differential |

| Internal PLL | Integrated clock multiplier with programmable divider |

| Offset drift | 0 ppm of FSR/°C |

| Offset error | −0.025% of FSR to +0.025% of FSR |

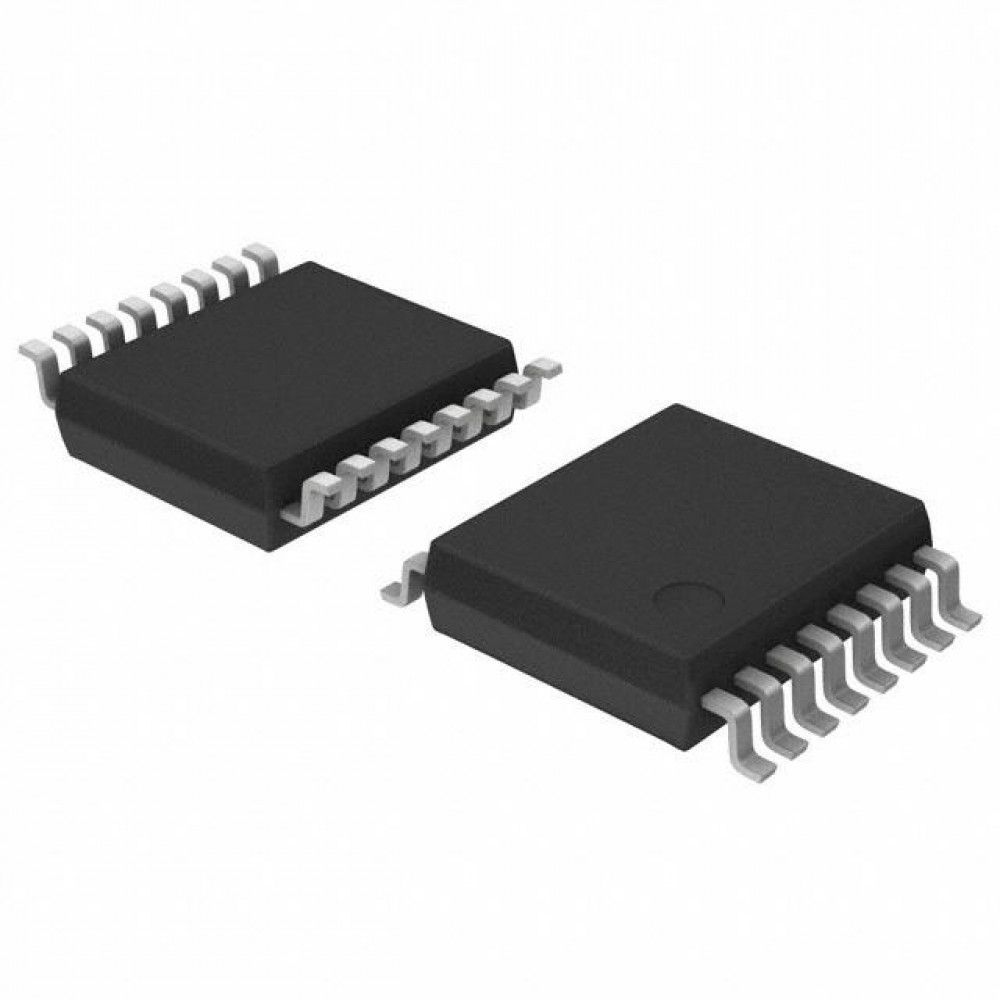

| Package type | 80-lead TQFP_EP (thin quad flat package, exposed pad, 12 mm × 12 mm) |

| Gain matching | −1% of FSR to +1% of FSR (±0.1% typ) |

| Clock input type | Differential or single-ended, sine or logic |

| Output resistance | 200 kΩ |

| Output capacitance | 3 pF |

| Data interface mode | Single-port interleaved / Dual-port |

| Interpolation rates | 2x / 4x / 8x |

| Data interface format | Twos complement / Straight binary |

| Output compliance range | -1.0 V to +1.25 V |

| Reference voltage drift | ±50 ppm/°C |

| Thermal resistance θJA | 23.5 °C/W |

| Digital modulation modes | None, fS/2, fS/4, fS/8 |

| Junction temperature max | 125 °C |

| Number of D/A converters | 2 |

| Clock input voltage range | 0 V to 3 V |

| Digital input capacitance | 5 pF |

| RESET pulse width minimum | 1.5 ns |

| Reference input resistance | 7 kΩ |

| Integral nonlinearity (INL) | ±6 LSB |

| Operating temperature range | -40 °C to +85 °C |

| Signal-to-noise ratio (SNR) | up to 79 dB |

| Supply voltage analog (AVDD) | 3.1 V to 3.5 V (3.3 V typ) |

| Analog supply current (IAVDD) | 72.5 mA typ, 76 mA max |

| Output noise (IOUTFS = 20 mA) | 50 pA/√Hz |

| SDIO output logic low voltage | 0.4 V |

| Supply voltage clock (CLKVDD) | 3.1 V to 3.5 V (3.3 V typ) |

| Supply voltage digital (DVDD) | 3.1 V to 3.5 V (3.3 V typ) |

| Digital supply current (IDVDD) | 34 mA typ, 41 mA max |

| Package specific ordering code | AD9777BSVZRL |

| SDIO output logic high voltage | DRVDD − 0.6 V |

| Clock input common-mode voltage | 0.75 V to 2.25 V |

| Differential nonlinearity (DNL) | −6.5 LSB to +6.5 LSB (±3 LSB typ) |

| Total harmonic distortion (THD) | −83 dB typ (fDATA = 100 MSPS, fOUT = 1 MHz, 0 dBFS) |

| Clock input differential voltage | 0.5 V to 1.5 V |

| Reference input compliance range | 0.1 V to 1.25 V |

| Reference small signal bandwidth | 0.5 MHz |

| Power supply rejection ratio AVDD | ±0.4% of FSR/V |

| Output rise/fall time (10% to 90%) | 0.8 ns |

| SDIO output logic high/low current | 30 mA to 50 mA |

| Serial port maximum SCLK frequency | 15 MHz |

| Analog supply current in SLEEP mode | 23.3 mA typ, 26 mA max |

| Gain drift (with internal reference) | 50 ppm of FSR/°C |

| Gain error (with internal reference) | −1.0% of FSR to +1.0% of FSR |

| Output settling time to 0.025% (tST) | 11 ns |

| Reference voltage (internal bandgap) | 1.20 V (1.14 V min, 1.26 V max) |

| Maximum DAC output update rate (fDAC) | 400 MSPS |

| Clock supply current (ICLKVDD, PLL ON) | 23.5 mA typ |

| Power dissipation in power-down (PWDN) | 6.0 mW |

| Clock supply current (ICLKVDD, PLL OFF) | 8.5 mA typ, 10.0 mA max |

| Full-scale output current range (IOUTFS) | 2 mA to 20 mA |

| Logic input low voltage (digital inputs) | 0 V min to 0.9 V max |

| Logic input high voltage (digital inputs) | 2.1 V min to 3 V typ |

| Maximum input data rate (no interpolation) | 160 MSPS |

| Serial port min clock pulse width high/low | 30 ns |

| Maximum power dissipation (PDIS, 400 MSPS, PLL on) | 1.75 W |

| Spurious-free dynamic range (baseband, to Nyquist) | up to 85 dBc |

| Nominal power dissipation (no interpolation, PLL off) | 380 mW typ, 410 mW max |

| Adjacent channel power ratio (ACPR, WCDMA 3.84 MHz, 5 MHz spacing) | 73 dBc |

Предлагаем ЦАП Analog Devices AD9777BSVZRL, 16-разрядный, двухканальный, интерполирующий TxDAC+ на выгодных условиях с полной технической поддержкой. Проверим наличие, поможем подобрать аналог.

Получить коммерческое предложение или оформить заказ:

8 800 301-96-04 info@fregat.ru

Для разработчиков новой продукции возможен заказ образца!