Texas Instruments DAC38RF84IAAV, одноканальный 14‑разрядный RF‑ЦАП 9 GSPS с JESD204B и PLL

| RoHS | Совместим |

| REACH | Совместим |

| ESD CDM, В | 250 |

Одноканальный высокоскоростной 14‑разрядный RF‑ЦАП с частотой дискретизации до 9 GSPS, интегрированным ФАПЧ/ГПД (VCO) на 6/9 ГГц и интерфейсом JESD204B (до 8 линий, 12,5 Гбит/с).

Обеспечивает прямую синтезу широкополосных сигналов в диапазоне 0…4,5 ГГц, имеет встроенный цифровой апконвертер с интерполяцией 6–24×, цифровой квадратурный модулятор с четырьмя 48‑битными NCO, блок защиты усилителя мощности и ЦАП с управляемым токовым выходом до 40 мА.

| RoHS | Совместим |

| REACH | Совместим |

| ESD CDM, В | 250 |

| ESD HBM, В | 1000 |

| JESD scrambling | Полиномиальный, 1+x^14+x^15, на пользовательских данных |

| RθJB, °C/Вт | 7.7 |

| Семейство | DAC38RFxx |

| Тип выхода | Одиночный (single‑ended) с интегрированным балуном |

| RθJC(top), °C/Вт | 1 |

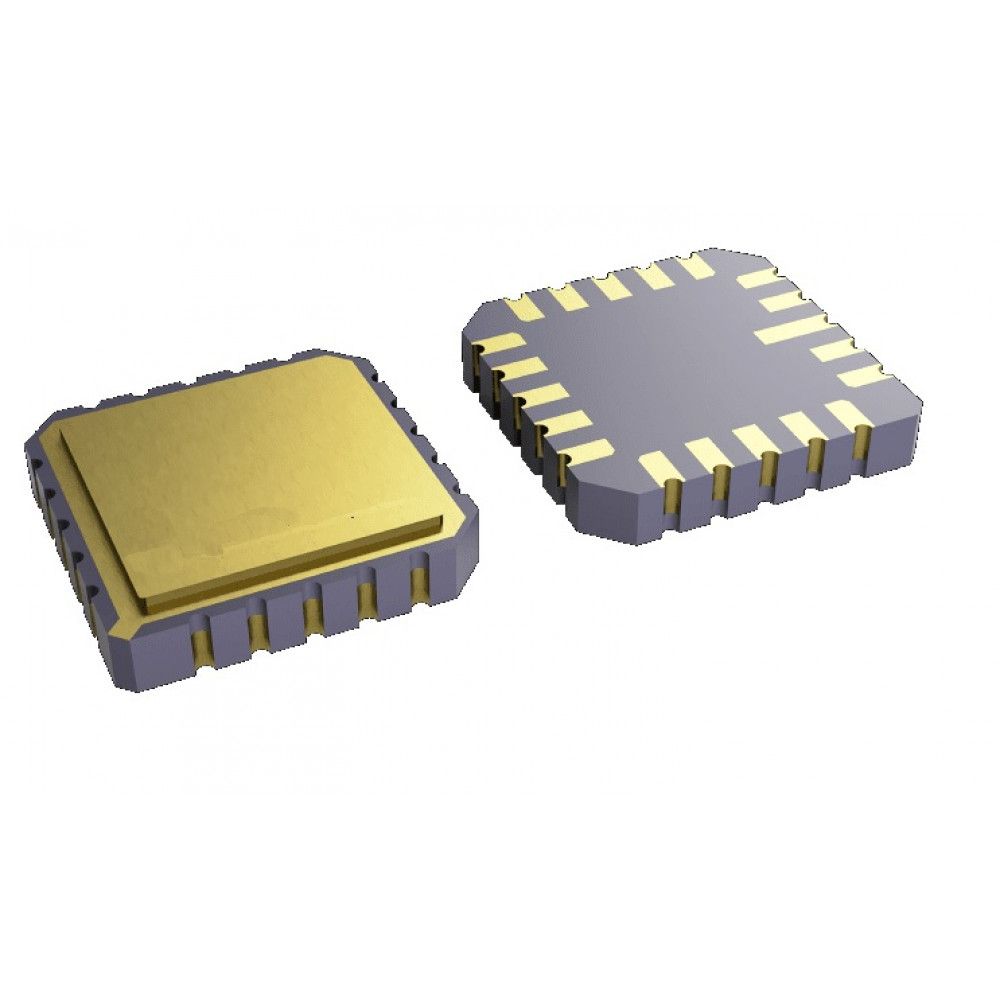

| Тип корпуса | FCBGA (Fine‑pitch Chip‑Scale BGA) |

| Интерполяция | 6×, 8×, 10×, 12×, 16×, 18×, 20×, 24× |

| Тип продукции | Catalog (серийный выпуск) |

| Полярность ALARM | По умолчанию активный низкий, настраиваемый |

| Шаг выводов, мм | 0.8 |

| Архитектура ЦАП | Источник тока (current‑source, выборочно‑токовый выход) |

| Полный партномер | DAC38RF84IAAV |

| WCDMA alt‑ACLR, тип., дБс | ≈77…83 |

| Типы встроенных PLL | Отдельная PLL для DAC и отдельная PLL для SerDes |

| Разрядность NCO, бит | 48 |

| Количество выводов | 144 |

| Разрешение ЦАП, бит | 14 |

| Типовые применения | Базовые станции 3G/4G/5G, радиолокация, SATCOM, измерительное и генераторное оборудование |

| Поддержка eye‑scan SerDes | 1 |

| Габариты корпуса, мм | 10×10 |

| Обозначение корпуса | AAV |

| Поддержка Subclass 1 (SYSREF) | 1 |

| Количество линий JESD204B | 8 |

| Поддержка IEEE1500 для SerDes | 1 |

| Интерфейс ввода данных | JESD204B, subclass 1 |

| Количество каналов ЦАП | 1 |

| Тип защиты от перегрева | Мониторинг температуры, без встроенного аппаратного отключения (по даташиту не указано иное) |

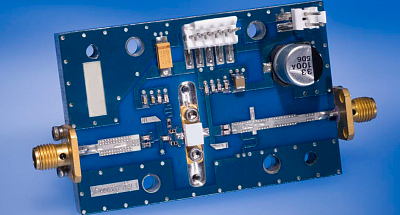

| Наличие оценочной платы | DAC38RF80EVM (поддерживает DAC38RF84) |

| Статус жизненного цикла | Active |

| Частоты грубого микшера | ±N·fDAC/8 (N по конфигурации) |

| Логические уровни CMOS IO, VIL | ≤0,3·VDDIO |

| Тип входов управления (SPI) | 3‑ или 4‑проводной последовательный интерфейс (SDIO/SDEN/SCLK/SDO) |

| Входной сердеc‑интерфейс | CML, дифференциальный, Rx[0..7]+/− с внутренним 100‑Ом терминатором |

| Количество независимых NCO | 4 |

| HD2 (2‑я гармоника), тип., дБс | ≈50–75 в зависимости от частоты/уровня |

| HD3 (3‑я гармоника), тип., дБс | ≈60–80 в зависимости от частоты/уровня |

| Наличие выходной задержки | 1 |

| Наличие блока защиты УМ (PAP) | 1 |

| Наличие грубого микшера (CMIX) | 1 |

| Шаг фазового сдвига eye‑scan, UI | 1/32 |

| Шаг фазового смещения NCO, бит | 16 |

| Максимальная скорость SerDes, Gbps | 12.5 |

| Наличие будильника/ALARM вывода | 1 |

| Фазовый шум VCO0 при 6 МГц, дБ/Гц | -146 |

| Фазовый шум VCO1 при 6 МГц, дБ/Гц | -148 |

| Наличие инверсного sinc‑фильтра | 1 |

| Фазовый шум VCO0 при 1,2 МГц, дБ/Гц | -131 |

| Фазовый шум VCO0 при 1,8 МГц, дБ/Гц | -135 |

| Фазовый шум VCO1 при 1,2 МГц, дБ/Гц | -131 |

| Фазовый шум VCO1 при 1,8 МГц, дБ/Гц | -136 |

| Максимальная высота корпуса, мм | 1.94 |

| Частота опорного сигнала PLL, МГц | 100…fVCO/4 (типично до 500) |

| Ширина полосы петли PLL (тип.), МГц | 0,5…~30 (зависит от настроек) |

| Количество выходных выводов ЦАП | 1 |

| Поддерживаемые режимы JESD204B (LMFSHd) | 82121, 42111/84111, 22210/44210, 12410/24410, 44210/88210, 24410/48410, 24310/48310 |

| Потребление в режиме Power‑down, мВт | ≈0,2…0,8 Вт |

| Тепловое сопротивление RθJA, °C/Вт | 25 |

| Частота тактового входа DACCLK, ГГц | 0,1…9 |

| Компенсационный резистор RBIAS, кОм | 3.6 |

| Интерфейс температурного датчика | Через SPI‑регистр, преобразование по тактам SCLK |

| Поддержка режимов Dual‑/Single‑channel DUC | Одноканальный DAC, но multi‑DUC с двумя путями AB/CD и суммированием |

| Тип входного тактового интерфейса | LVPECL/LVDS‑совместимый дифференциальный |

| Время установления выхода до 0,1%, нс | 1 |

| Номинальные частоты центров VCO, ГГц | 5,9 и 8,85 |

| Поддерживаемые режимы скорости SerDes | полная, 1/2, 1/4, 1/8 от полной |

| Поддерживаемые тестовые режимы SerDes | PRBS7, PRBS23, PRBS31, чередование 0/1, пользовательский 20‑битный шаблон |

| WCDMA ACLR, fDAC≈5,898 ГГц, fOUT=0,95/2,14 ГГц, дБс | ≈75…76 |

| Максимальная скорость линии JESD204B, Gbps | 12.5 |

| Питание цифрового ввода/вывода VDDIO, В | 1.8 |

| Наличие блока выходного усиления (GAIN) | 1 |

| IMD3 (два тона, −6 dBFS, Δf=10 МГц), тип., дБс | ≈68–84 |

| Инверсия полярности выхода (2’s complement) | 1 |

| Наличие делителя выходного такта (CLKTX) | Да, делители /2, /3, /4 |

| SFDR в полосе ±250 МГц вокруг fOUT, тип., дБс | до ≈90–100 |

| Логические уровни CMOS IO (при VDDIO=1,8 В), VIH | ≥0,7·VDDIO |

| Максимальное напряжение питания 1 В, V | до 1,3 |

| Максимальное отрицательное питание, В | -2…0,3 |

| Поддержка многочиповой синхронизации | 1 |

| Выходное напряжение логики VOL при +2 мА | ≤0,5 В |

| Диапазон отрицательного питания VEE18N, В | -1,89…-1,71 |

| Максимальная температура кристалла, °C | 125 |

| Полный выходной ток IOUTFS, мин/ном/макс, mA | 10 / 30 / 40 |

| Тип выходного тактового интерфейса CLKTX | CML, дифференциальный, внутренняя терминация 100 Ом |

| Диапазон рабочих температур корпуса, °C | -40…+85 |

| Максимальное напряжение питания 1,8 В, V | до 2,45 |

| Фазовый шум VCO0 (5,9 ГГц) при 600 кГц, дБ/Гц | -124 |

| NSD при 6 ГГц такте, fOUT≈0,5…2,65 ГГц, дБFS/Гц | от ≈‑170 до ≈‑155 |

| NSD при 9 ГГц такте, fOUT≈0,5…3,65 ГГц, дБFS/Гц | от ≈‑172 до ≈‑153 |

| Выходное напряжение логики VOH при −2 мА | ≥0,8·VDDIO |

| Диапазон частот NCO (относительно fDAC), ГГц | 0…fDAC/2 |

| LTE 20 МГц ACLR, fDAC≈8,847 ГГц, fOUT до 3,7 ГГц, дБс | ≈63…74 |

| Размер окна усреднения PAP (выбор), выборки | 32 / 64 / 128 |

| NSD (Noise Spectral Density) при fDAC=9 GSPS, fOUT=1,8 ГГц, dBc/Hz | -157 |

| Диапазон общего уровня тактового входа, В | около 0,5 |

| Диапазон выходного коэффициента усиления | 0…>1, формат фиксированной точки |

| Диапазон выходного соответствия (compliance), В | 1,3…2,3 |

| Время перехода в глубокий сон до <1% IOUTFS, мкс | 90 |

| SFDR (0–fDAC/2), тип., fDAC=9 ГГц, fOUT≈0,5…3,65 ГГц, дБс | ≈50…70 в зависимости от частоты |

| Максимальная частота дискретизации ЦАП, GSPS | 9 |

| Диапазон синтезируемых выходных частот, ГГц | 0…4,5 |

| Минимальные времена setup/hold SYSREF к DACCLK (тип.), пс | 50 |

| Наличие встроенного температурного датчика | 1 |

| Разрядность АЦП температурного датчика, бит | 8 |

| Диапазон выходной цифровой задержки, такты DAC | 0…15 |

| Погрешность коррекции sinc в полосе до 0,4·fDAC, дБ | < 0,03 |

| Поддержка SYSREF (LVPECL), входное сопротивление, Ом | 100 |

| Время включения DAC из глубокого сна до 1% IOUTFS, мкс | 90 |

| Наличие цифрового квадратурного модулятора (DQM) | 1 |

| Пиковая температура переход‑корпус (Absolute Max), °C | 150 |

| Диапазон потребляемой мощности (режимы 1–10), мВт | ≈2195…4894 в зависимости от режима |

| Рекомендуемая рабочая температура кристалла, °C | до 105 |

| Фазовый шум VCO1 (8,85 ГГц) при смещении 600 кГц, дБ/Гц | -123 |

| Диапазон смещения порога по напряжению в eye‑scan, мВ | около −310…+300 c шагом ≈10 мВ |

| Неприведённые параметры AC/цифровых характеристик | См. оригинальный даташит TI SLASEA3D (Rev. D) для полной таблицы |

| Диапазон дифференциального входного уровня CML RX, mVpp | 50…1200 |

| Диапазон питания цифрового ядра, V (VDDDIG1, VDDLx, VDDCLK1 и др.) | 0,95…1,05 |

| Дифференциальное тактовое входное сопротивление, Ом | 100 |

| Настраиваемый шаг изменения PAP‑коэффициента, формат | фиксированная точка, 1,0 соответствует «1000000000b» |

| Типичное энергопотребление (характерные режимы), мВт | ≈3,1…4,6 Вт |

| Совместимость по выводам с другими членами семейства | Пин‑совместим с DAC38RF80/90 в корпусе AAV |

| Внутреннее дифференциальное сопротивление входа SerDes, Ом | 85…115 (ном. 100) |

| Диапазон питания аналоговых узлов 1,8 В, V (VDDA18, VDDAVCO18 и др.) | 1,71…1,89 |

| Диапазон рабочих частот встроенного VCO, низкий диапазон, ГГц | 5,24…6,72 |

| Диапазон рабочих частот встроенного VCO, высокий диапазон, ГГц | 7,96…9,0 |

| Максимальная комплексная скорость входных данных на канал, MSPS | 1250 |

| Цифровая задержка от JESD‑буфера до выхода ЦАП, циклы такта DAC (диапазон) | от ~816 до ~2941 в зависимости от LMFS и интерполяции |

Предлагаем Texas Instruments DAC38RF84IAAV, одноканальный 14‑разрядный RF‑ЦАП 9 GSPS с JESD204B и PLL на выгодных условиях с полной технической поддержкой. Проверим наличие, поможем подобрать аналог.

Получить коммерческое предложение или оформить заказ:

8 800 301-96-04 info@fregat.ru

Для разработчиков новой продукции возможен заказ образца!