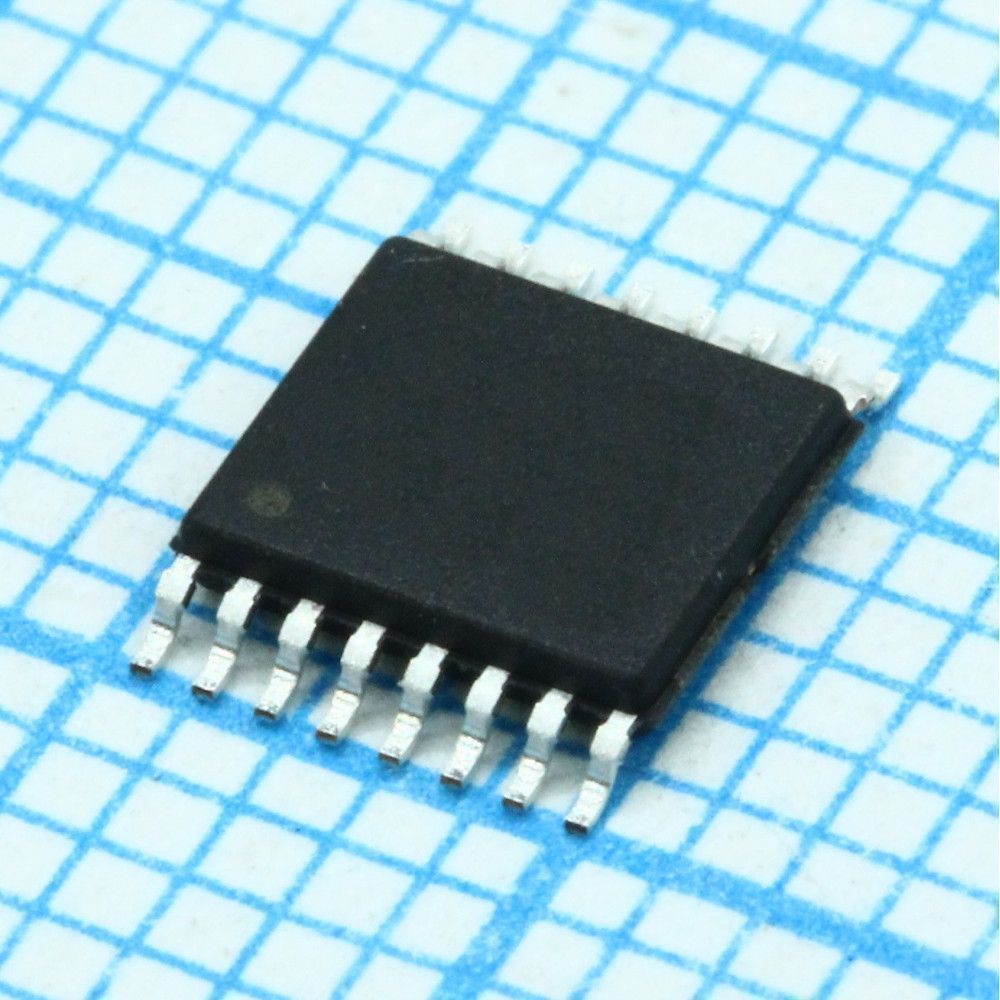

Texas Instruments DAC8554IPWR, 4-канальный 16-разрядный ЦАП

| SINAD | 84 дБ |

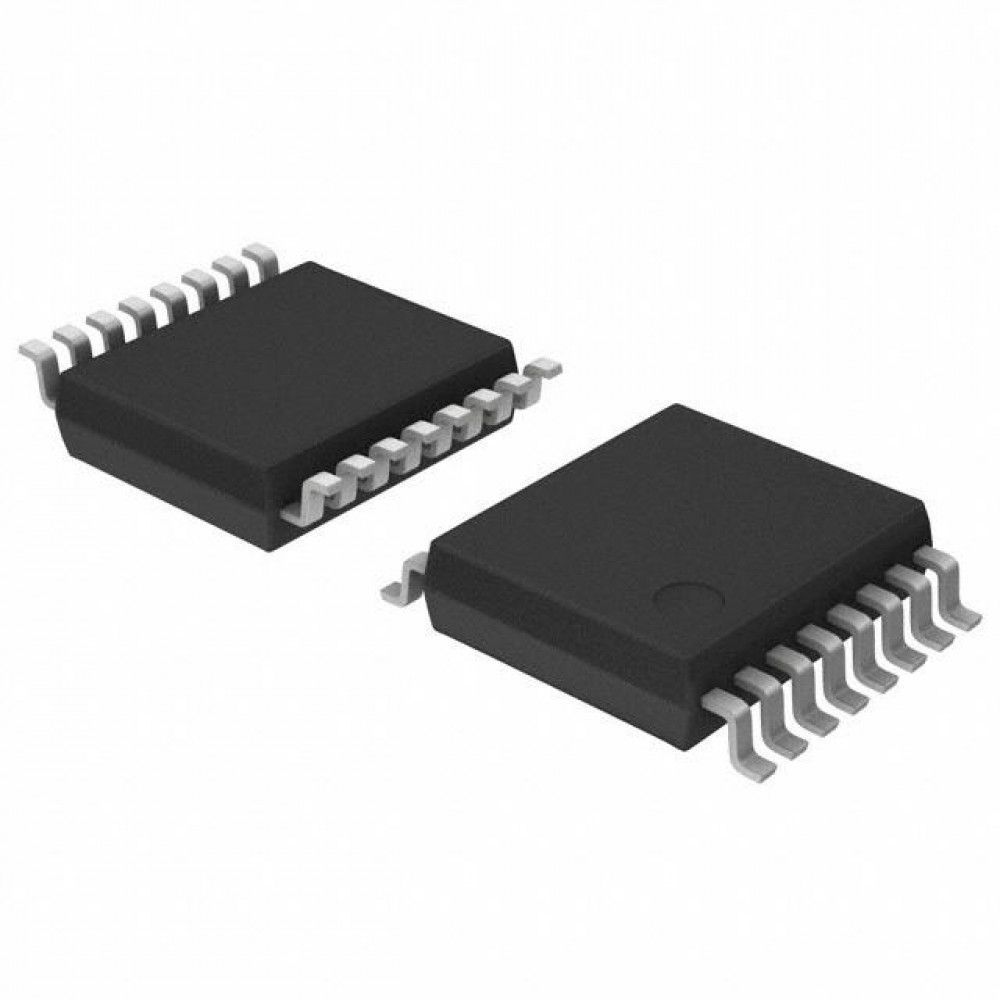

| Корпус | TSSOP-16 (Thin Shrink Small Outline Package) |

| КПД (Efficiency) | 89% (при IL=2 мА, AVDD=5 В) |

Микросхема использует архитектуру на базе резистивной цепи с встроенным операционным усилителем, обеспечивающим полнодиапазонный выходной сигнал (Rail-to-Rail) в диапазоне питания 2,7–5,5 В.

Особенностью устройства является низкий импульсный шум на выходе (0,15 нВ·с), точность 4 LSB, и низкое потребление (150 мкА на канал при 2,7 В).

Интерфейс реализован на стандарте SPI/DSP.

Устройство содержит встроенную схему сброса при включении в ноль и механизм независимого отключения каждого канала с несколькими режимами (высокое сопротивление, 1 кОм, 100 кОм).

Предназначен для мобильных приборов, систем управления, сбора данных и программируемых средств ослабления сигнала.

| SINAD | 84 дБ |

| Корпус | TSSOP-16 (Thin Shrink Small Outline Package) |

| КПД (Efficiency) | 89% (при IL=2 мА, AVDD=5 В) |

| Режим Broadcast | Одновременное обновление 16 каналов (4 микросхемы × 4 канала) |

| Архитектура | Резистивная цепь (String DAC) с буферным усилителем на выходе |

| Разрядность | 16 бит |

| Режимы Power-Down | Высокое сопротивление (Hi-Z), 1 кОм±20%, 100 кОм±20%, Hi-Z (повторный) |

| Тип упаковки | Tape & Reel (лента и катушка) |

| Монотонность | 16-разрядная монотонность в диапазоне температур |

| Размер корпуса | 4,4 мм × 5,1 мм × макс. 1,175 мм |

| Режимы адресации | 4 отдельных устройства на одной SPI шине (благодаря адресным контактам A0, A1) |

| Диапазон хранения | -65 до +150 °C |

| Количество каналов | 4 |

| Серийный интерфейс | SPI совместимый, 3-проводной (SYNC, SCLK, DIN) |

| Ошибка полной шкалы | ±0,3% FSR (тип.), ±0,5% FSR (макс.) |

| Сброс при включении | Все выходы устанавливаются в нуль (0 В) при подаче питания |

| Обозначение корпуса | PW |

| Скорость нарастания | 1,8 В/мкс |

| Количество контактов | 16 |

| Количество в упаковке | 2000 шт. |

| Время цикла SCLK (2,7–3,6 В) | 40 нс |

| Время цикла SCLK (3,6–5,5 В) | 20 нс |

| Минимальное время SYNC HIGH | 20 нс (при 3,6–5,5 В), 40 нс (при 2,7–3,6 В) |

| Мощность в режиме Power-Down | 4 мкВт |

| Совместимость с логикой | CMOS логика 1,8–5,5 В (с буферизацией уровня IOVDD) |

| Ошибка нулевого масштаба | ±2 мВ (тип.), ±12 мВ (макс.) |

| Ёмкость логического входа | 3 пФ |

| Коэффициент сигнал-шум (SNR) | 95 дБ |

| Относительная точность (INL) | ±4 LSB (тип.), ±12 LSB (макс.) |

| Питание цифровой части (IOVDD) | 1,8–5,5 В |

| Ширина сдвигового регистра | 24 бита (8 бит управления + 16 бит данных) |

| Короткозамкнутый ток (AVDD=3 В) | 20 мА |

| Короткозамкнутый ток (AVDD=5 В) | 50 мА |

| Диапазон рабочих температур | -40 до +105 °C |

| Питание аналоговой части (AVDD) | 2,7–5,5 В |

| Ошибка коэффициента усиления | ±0,05% FSR (тип.), ±0,15% FSR (макс.) |

| Время установления (до ±0,003% FSR) | 8–10 мкс (при CL=200 пФ), 12 мкс (при CL=500 пФ) |

| Диапазон выходного напряжения | 0–VREFH В (Rail-to-Rail) |

| Дрейф ошибки нулевого масштаба | ±5 мкВ/°C |

| Максимальная ёмкостная нагрузка | 1000 пФ |

| Максимальное напряжение выходов | -0,3 до (AVDD+0,3) В |

| Стабильность ёмкостной нагрузки | Стабилен при нагрузке до 1000 пФ |

| Импульсный шум на выходе (Glitch Energy) | 0,15 нВ·с |

| Минимальная резистивная нагрузка | 2 кОм (параллельно с 1000 пФ) |

| Дифференциальная нелинейность (DNL) | ±0,25 LSB (тип.), ±1 LSB (макс.) |

| Паразитная связь постоянного тока | 0,25 LSB |

| Время выхода из режима Power-Down (AVDD=3 В) | 5 мкс |

| Время выхода из режима Power-Down (AVDD=5 В) | 2,5 мкс |

| Полное гармоническое искажение (THD) | -85 дБ |

| Функция одновременного обновления | Программное (через SPI) и аппаратное (через LDAC) |

| Коэффициент подавления питания (PSRR) | 0,75 мВ/В |

| Мощность при 5 В (все каналы активны) | 4,25 мВт |

| Температурный коэффициент усиления | ±1 ppm/°C |

| Потребление в режиме Power-Down (AVDD=2,7–3,6 В) | 0,4–2 мкА |

| Потребление в режиме Power-Down (AVDD=3,6–5,5 В) | 0,7–2 мкА |

| Максимальная частота SCLK (IOVDD=AVDD=2,7–3,6 В) | 25 МГц |

| Максимальная частота SCLK (IOVDD=AVDD=3,6–5,5 В) | 50 МГц |

| Потребление тока одного канала при 2,7 В | 150 мкА |

| Паразитная связь переменного тока (1 кГц) | -100 дБ (тип.) |

| Выходное сопротивление постоянного тока | 1 Ом (в точке среднего масштаба) |

| Максимальная температура переходов (Tj max) | 150 °C |

| Максимальное напряжение цифровых входов | -0,3 до (AVDD+0,3) В |

| Тепловое сопротивление корпус-воздух (θJA) | 118 °C/Вт |

| Тепловое сопротивление корпус-переход (θJC) | 29 °C/Вт |

| Максимальное напряжение AVDD относительно GND | -0,3 до +6 В |

| Входное сопротивление эталонного напряжения | 31 кОм |

| Напряжение логического входа LOW (VIL, IOVDD=2,7–5,5 В) | 0–0,3·IOVDD В |

| Потребление тока (нормальный режим, AVDD=2,7–3,6 В) | 0,6–0,9 мА |

| Потребление тока (нормальный режим, AVDD=3,6–5,5 В) | 0,65–0,95 мА |

| Напряжение логического входа HIGH (VIH, IOVDD=2,7–5,5 В) | 0,7·IOVDD–IOVDD В |

| Ток входа положительного эталона (при VREFH=AVDD=3 В) | 120–200 мкА |

| Ток входа положительного эталона (при VREFH=AVDD=5 В) | 180–250 мкА |

| Динамический диапазон без связанных гармоник (SFDR) | 87 дБ |

| Цифровой шум на выходе (при смене соседних каналов) | 0,15 LSB |

| Защита от электростатического разряда (ESD) — Human Body Model | 1500 В |

| Защита от электростатического разряда (ESD) — Charged Device Model | 1000 В |

| Минимальное время от 24-го фронта SCLK до следующего фронта SYNC | 130 нс |

Предлагаем Texas Instruments DAC8554IPWR, 4-канальный 16-разрядный ЦАП на выгодных условиях с полной технической поддержкой. Проверим наличие, поможем подобрать аналог.

Получить коммерческое предложение или оформить заказ:

8 800 301-96-04 info@fregat.ru

Для разработчиков новой продукции возможен заказ образца!